糖尿病になってから足の裏がずっと痺れていて、まるで砂利の上を歩いているようでした。この対処法を始めて痺れが軽くなり、普通に歩けるようになりました。おかげでパートの立ち仕事も続けられています。本当にありがたいです。

左記クレジットカード、銀行振込、コンビニ決済に対応

更新日:2025/4/11

| 個数 | 販売価格(1錠あたり) | 販売価格(箱) | ポイント | 購入 |

|---|---|---|---|---|

| 100錠 | 60円 | 6,060円 | 181pt |

| 個数 | 販売価格(1錠あたり) | 販売価格(箱) | ポイント | 購入 |

|---|---|---|---|---|

| 50錠 | 103円 | 5,160円 | 154pt |

| 個数 | 販売価格(1錠あたり) | 販売価格(箱) | ポイント | 購入 |

|---|---|---|---|---|

| 50錠 | 117円 | 5,860円 | 175pt | |

| 100錠 | 98円 | 9,860円 | 295pt |

| 個数 | 販売価格(1錠あたり) | 販売価格(箱) | ポイント | 購入 |

|---|---|---|---|---|

| 50錠 | 135円 | 6,760円 | 202pt | |

| 100錠 | 122円 | 12,260円 | 367pt |

①1万円以上で送料無料

1回の注文で10,000円以上だった場合、1,000円の送料が無料となります。

まとめ買いをすると1商品あたりのコストパフォーマンスが高くなるためおすすめです。

②プライバシー守る安心梱包

外箱に当サイト名や商品名が記載されることはないため、ご家族や配達員など第三者に内容を知られることは御座いません。

③100%メーカー正規品取り扱い

当サイトの商品は100%メーカー正規品となっており、第三者機関による鑑定も行っております。

商品の破損などがあった場合は再配送などにて対応させて頂きますので、ご連絡頂ければ幸いです。

④いつでも購入可能 処方箋不要

サイト上では24時間いつでもご注文を受けております。

また、お電話によるご注文も受け付けておりますのでネットが苦手な方はお気軽にどうぞ。

⑤商品到着100%

商品発送後はお荷物の追跡状況が分かる追跡番号をご案内させて頂きます。

郵便局には保管期限がありますのでご注意ください。

・自宅配達で不在だった場合の保管期限・・・16日間前後

・郵便局留めとした場合の保管期限・・・7~30日間

⑥コンビニ決済利用可能

ご近所のコンビニにていつでもお支払可能です。

セブンイレブンに限り店舗での機械操作を必要とせず、手続き完了後に表示されるバーコードや払込票番号をレジに提示することでお支払い頂けます。

うつ症状の改善

10mgx100錠

3,560円

うつ症状の改善

10mgx28錠

4,560円

うつ症状の改善

50mgx100錠

7,260円

うつ症状の改善

25mgx100錠

3,960円

うつ症状の改善

20mgx28錠

4,560円

うつ症状の改善

60mgx28錠

7,160円

うつ症状の改善

100mgx30錠

4,860円

うつ症状の改善

25mgx100錠

5,460円

うつ症状の改善

5mg28錠x1箱

4,860円

うつ症状の改善

20mg200錠x1箱

11,960円

うつ症状の改善

15mgx100錠

6,560円

うつ症状の改善

15mgx28錠

4,960円

サインバルタ・ジェネリック 20mg x 100錠

6,060円

ポイント:181pt

10,000円以上購入で送料無料

在庫あり

糖尿病になってから足の裏がずっと痺れていて、まるで砂利の上を歩いているようでした。この対処法を始めて痺れが軽くなり、普通に歩けるようになりました。おかげでパートの立ち仕事も続けられています。本当にありがたいです。

個人輸入の良い所は自分の予算に合わせたり、好きな薬を選べること。だけど、自己判断で決めて買うから自分に合うかどうかは試してみないとわからない。サインバルタのジェネリックを1週間くらい続けて飲んでみたけど、副作用に耐えられないから飲むのをやめた。

はい、うつ症状だけでなく、不安感やそわそわした気持ちにも効果が期待できます。気持ちが落ち着きやすくなります。

サインバルタは、全身に原因のはっきりしない痛みが続く線維筋痛症にも効果が認められています。痛みの感じ方をやわらげることで、生活の質を改善するサポートが期待できます。

直接眠くする薬ではありませんが、気分が安定することで夜にリラックスできるようになり、自然に眠れるようになったと感じる人もいます。

はい、慢性腰痛症などの痛み治療において、ほかの鎮痛薬と併用せず単独で使用されることもあります。神経の痛みに特化して働くのが特徴です。

基本的に朝に飲むことが推奨されています。夜に飲むと、まれに眠気を感じにくくなったり、睡眠リズムに影響することがあるため、できるだけ朝に飲むのがよいとされています。

服用量を自己判断で増やしたり減らしたりしてはいけません。効果や副作用を見ながら、医師の指示で調整することが必要です。

だいたい1〜2週間ほどで気分や痛みの改善を感じ始める人が多いです。ただし、効果の出方には個人差があり、焦らずに飲み続けることが大切です。

サインバルタ・ジェネリックを飲んでいる間の過度な飲酒は控えたほうがいいです。過度な飲酒をしてしまうと肝障害が悪化してしまう可能性があるため、お酒はできる限り控えるようにしましょう。

まれにふらつきや立ちくらみが起こることがあります。急に立ち上がる動作を避けるなど注意し、症状が強い場合は必ず先生に相談してください。

ごくまれに、けいれんが起こることが報告されています。異常な体の震えや意識障害が現れた場合は、すぐに医療機関を受診してください。

サインバルタでは、比較的よく口の渇き(ドライマウス)が起こることがあります。のどの渇きが強い場合は、水分をこまめにとるなどして対応しましょう。

高齢者がサインバルタを使用する場合は、めまい、転倒などのリスクが高くなる可能性があるため、特に慎重に様子を見ながら治療を行う必要があります。

| 1日の服用回数 | 1回 |

|---|---|

| 1回の服用量 | 40mg |

| 服用のタイミング | 朝食後 |

| 服用間隔 | 毎日 |

| 1日の服用回数 | 1回 |

|---|---|

| 1回の服用量 | 60mg |

| 服用のタイミング | 朝食後 |

| 服用間隔 | 毎日 |

| 商品名 | コントミン・ジェネリック | レクサプロ・ジェネリック | チアプリダール | アゴプレックス | トレドミン・ジェネリック | ティアプレックス | セントジョーンズワート | ウェルブトリンXL |

|---|---|---|---|---|---|---|---|---|

| 商品画像 |  |  |  |  |  |  |  |  |

| 特徴1 | ・不安感や興奮状態を鎮める作用に優れている | ・症状に応じて3種類から選べる | ・過剰なドパミンの神経伝達を抑える | ・睡眠障害にも効果が期待できる | ・穏やかな効き目で効き方も速い | ・さまざまな精神症状に応用されている有効成分を配合 | ・軽度から中等度のうつ病の治療に有効 | ・脳内のドーパミンの働きを増強 |

| 特徴2 | ・ほかの脳内物質系の神経を抑える作用もある | ・1回の服用で効果が長く続く | ・心を穏やかにする | ・従来品よりもさらに副作用の心配が少ない | ・飲み合わせが悪い医薬品が少なく使いやすい | ・病院で処方されているグラマリール錠と同成分 | ・うつ病に伴う不眠症の改善にも期待できる | ・憂うつな気分をやわらげる |

| 内容量 | 100mgx100錠 | 5mgx100錠 | 100mg20錠x1箱 | 25mg50錠x1箱 | 25mgx100錠 | 25mg100錠x1箱 | 375mg120錠x1本 | 300mg30錠x1箱 |

| 価格 | 2,700円 | 3,560円 | 3,960円 | 6,560円 | 5,260円 | 4,160円 | 4,260円 | 4,960円 |

| 5%以上 | 1〜5%未満 | 1%未満 | 頻度不明 | |

| 過敏症 | 発疹、そう痒、蕁麻疹 | 接触性皮膚炎、光線過敏反応、血管浮腫、皮膚血管炎 | ||

| 全身症状 | 倦怠感 | ほてり、発熱、悪寒、脱水、脱力感 | ||

| 精神神経系 | 傾眠(24.3%)、頭痛、めまい | 不眠、立ちくらみ、しびれ感、振戦、浮遊感 | あくび、焦燥感、気分高揚、注意力障害、錐体外路症状、不安、異常夢(悪夢を含む)、頭がぼーっとする、性欲減退、躁病反応、錯感覚、無感情、味覚異常 | 激越、オーガズム異常、嗜眠、睡眠障害、歯軋り、失見当識、攻撃性、怒り、歩行障害、開口障害、下肢静止不能症候群、異常感 |

| 消化器 | 悪心(22.4%)、食欲減退、口渇(12.8%)、便秘(12.4%)、下痢 | 腹部痛、嘔吐、腹部膨満感、腹部不快感、消化不良、胃炎 | 口内炎、歯痛、胃腸炎、咽頭不快感 | 咽頭炎、咽喉緊張、口臭、嚥下障害、顕微鏡的大腸炎 |

| 感覚器 | 耳鳴 | 視調節障害、眼乾燥、霧視、耳痛 | 散瞳、緑内障 | |

| 循環器 | 動悸、頻脈、血圧上昇 | 起立性低血圧、上室性不整脈、失神 | ||

| 肝臓 | AST上昇、ALT上昇、γ-GTP上昇、総ビリルビン上昇、Al-P上昇、LDH上昇 | |||

| 血液 | ヘモグロビン減少、赤血球減少、ヘマトクリット減少、鼻出血 | 異常出血(斑状出血、胃腸出血等)、白血球減少 | ||

| 筋・骨格系 | 背部痛、関節痛、筋痛、肩こり、筋痙攣 | 筋緊張 | ||

| 泌尿器・生殖器 | 排尿困難 | 性機能異常(月経異常、射精障害、勃起障害等)、排尿障害、血中クレアチニン上昇、BUN上昇、頻尿、尿中アルブミン/クレアチニン比上昇、尿流量減少 | 多尿、閉経期症状、精巣痛 | |

| 代謝・内分泌 | 高血糖、トリグリセリド上昇、総コレステロール上昇、尿中蛋白陽性 | 血中カリウム減少 | 甲状腺機能低下、低ナトリウム血症、乳汁漏出症、高プロラクチン血症、血中カリウム上昇 | |

| その他 | 発汗、体重減少、体重増加、CK(CPK)上昇 | 浮腫、冷感、熱感、呼吸苦、胸痛、冷汗、咳嗽 |

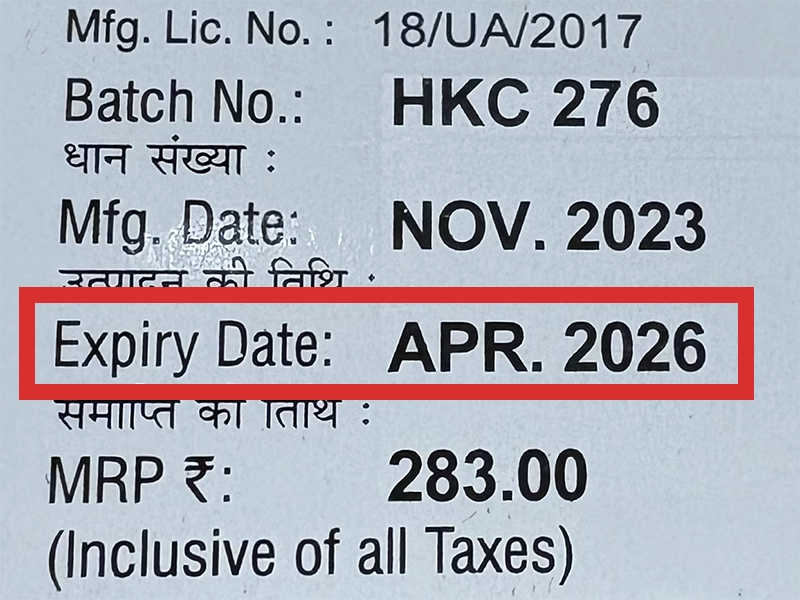

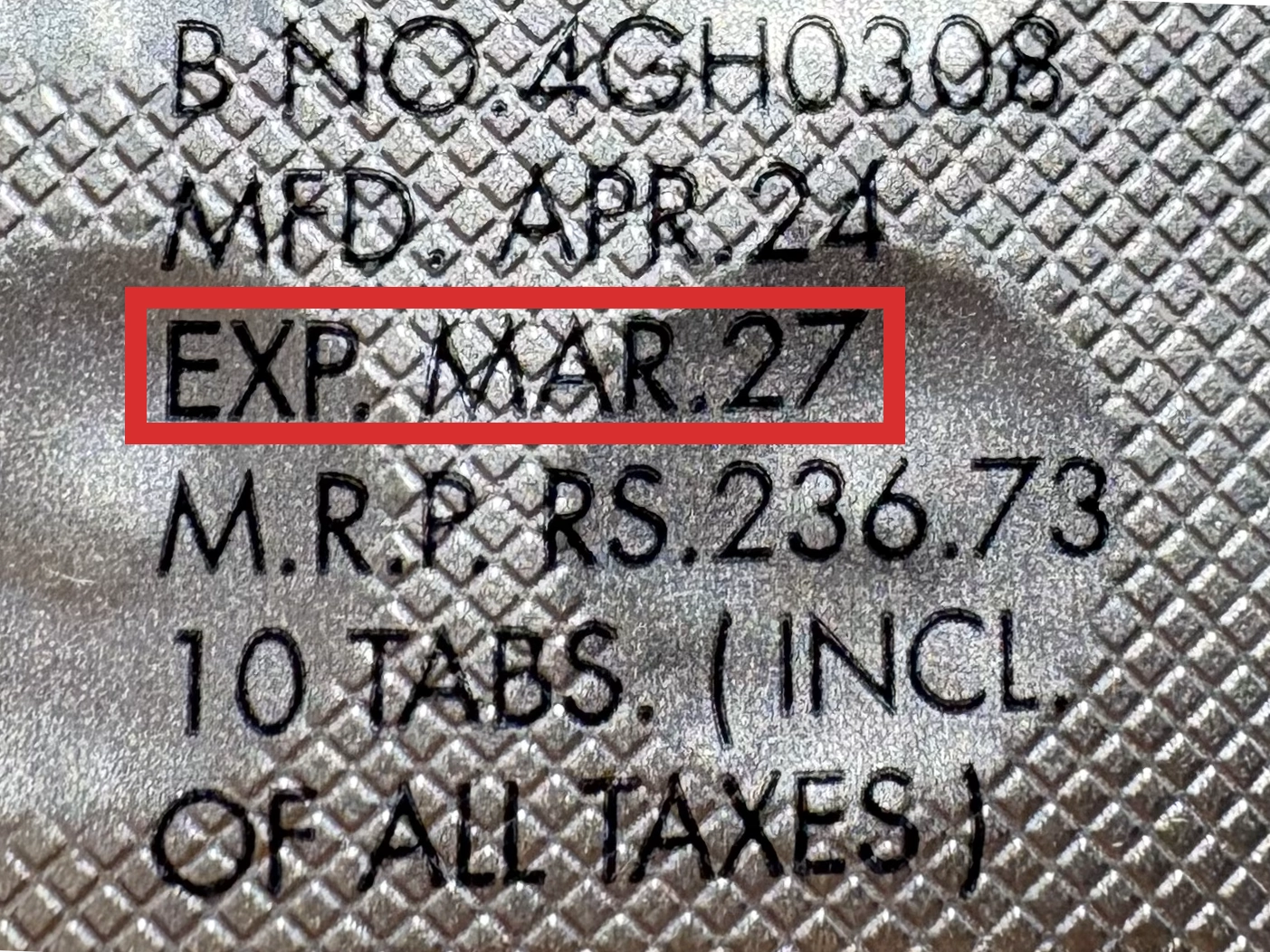

本製品は海外製のため、期限表記が日本と異なる場合がございます。

パッケージ裏面や側面、シートなどに以下のような表記がされています。

| EXP | 使用期限 例:EXP 12/2025→2025年12月まで使用可 |

|---|---|

| MFG または MFD | 製造日 例:MFG 03/2023 |

| BEST BEFORE | 品質が最も安定している目安日 |

※国や製品により日付の並び(例:月/年、日/月/年)が異なる場合がありますのでご注意ください

EXP(Expiry Date) の表記がなく、MFG または MFDしか記載がないケースがあります。

この場合は MFG(MFD) から2~3年が使用期限の目安です。

※「LOT」や「BATCH」の表記は製造番号であり期限ではありません。

パッケージ例となります。

商品やご注文単位によってはシート単位でのお届けとなる場合が御座います。

外箱に当サイト名や商品名が記載されることはないため、ご家族や配達員など第三者に内容を知られることは御座いません。

糖尿病になってから足の裏がずっと痺れていて、まるで砂利の上を歩いているようでした。この対処法を始めて痺れが軽くなり、普通に歩けるようになりました。おかげでパートの立ち仕事も続けられています。本当にありがたいです。

大学に行く気力もなく、部屋に引きこもる毎日でした。このケアを始めてから、少しずつ外に出る勇気が出て、友達とも会えるように。頭の中のモヤモヤも晴れてきた感じです。もう一度頑張ってみようと思えます。

もう何年も腰痛に悩まされ、湿布や痛み止めもあまり効かず…。これを試してから、日常生活での痛みがかなり軽減されました。長時間座っていても辛くなくなり、趣味の裁縫もまた楽しめるように!嬉しいです。

飲み続けていたら副作用を感じなくなった!うつ症状が少しずつ軽くはなってきてるから、薬はちゃんと効いてるみたい!買って良かった!

薬に手を出すか迷っていましたが、今の状態を少しでも改善できるならと思い、購入させてもらいました。服用し始めて数日なので、効き目はあまりわかりません。副作用で軽い頭痛は感じてしまいますが、このまま飲み続けて、どれだけ改善できるか試してみようと思います。

商品口コミの投稿は会員のみ行えるようになっております。

お手数ですが会員ログインの上でご投稿頂きますようお願いいたします。

口コミをご投稿頂いたお客様にはポイントをプレゼントさせて頂いております。

文章のみであれば100ポイント、文章+写真付きのものは300ポイントをプレゼントさせて頂きます。

規約や詳細などはこちらをご確認くださいませ。