「有効性と安全性」「高齢者の方でも」の言葉に惹かれました。血圧の薬は検診の数値で効果を確認できるので、実感できてわかりやすい。今回も良い結果だったので家族も安心してくれています。

左記クレジットカード、銀行振込、コンビニ決済に対応

更新日:2025/6/15

| 個数 | 販売価格(1箱あたり) | 販売価格(箱) | ポイント | 購入 |

|---|---|---|---|---|

| 1箱 | 4,960円 | 4,960円 | 148pt | |

| 2箱 | 3,280円 | 6,560円 | 196pt |

①1万円以上で送料無料

1回の注文で10,000円以上だった場合、1,000円の送料が無料となります。

まとめ買いをすると1商品あたりのコストパフォーマンスが高くなるためおすすめです。

②プライバシー守る安心梱包

外箱に当サイト名や商品名が記載されることはないため、ご家族や配達員など第三者に内容を知られることは御座いません。

③100%メーカー正規品取り扱い

当サイトの商品は100%メーカー正規品となっており、第三者機関による鑑定も行っております。

商品の破損などがあった場合は再配送などにて対応させて頂きますので、ご連絡頂ければ幸いです。

④いつでも購入可能 処方箋不要

サイト上では24時間いつでもご注文を受けております。

また、お電話によるご注文も受け付けておりますのでネットが苦手な方はお気軽にどうぞ。

⑤商品到着100%

商品発送後はお荷物の追跡状況が分かる追跡番号をご案内させて頂きます。

郵便局には保管期限がありますのでご注意ください。

・自宅配達で不在だった場合の保管期限・・・16日間前後

・郵便局留めとした場合の保管期限・・・7~30日間

⑥コンビニ決済利用可能

ご近所のコンビニにていつでもお支払可能です。

セブンイレブンに限り店舗での機械操作を必要とせず、手続き完了後に表示されるバーコードや払込票番号をレジに提示することでお支払い頂けます。

ニディカード 10mg30錠 x 1箱

4,960円

ポイント:148pt

10,000円以上購入で送料無料

在庫あり

「有効性と安全性」「高齢者の方でも」の言葉に惹かれました。血圧の薬は検診の数値で効果を確認できるので、実感できてわかりやすい。今回も良い結果だったので家族も安心してくれています。

血圧を下げるために飲んでいるのに、血圧が一向に下がってくれません。血圧高めの方が書き込んでいる口コミなどでは高評価になっていたんですが、やはり口コミを信用しすぎたんでしょうかね。まだ少し余っているので残りも飲み切るようにしていきますが、これでもほとんど変わりが無いようでしたら、他の薬購入するか病院で診てもらって薬を処方してもらうようにします。

高血圧薬は血管を広げて血圧を下げる作用があります。しかしながら、高血圧の原因に対してのアプローチはありません。そのため、高血圧の薬は対症療法となるため生活習慣の改善など高血圧の原因の改善ができない場合にはその可能性はあります。

高血圧の薬は血圧を下げるものであるため、ED薬の作用と重複してしまい、過度な血圧低下を引き起こしてしまうおそれがあります。そのため、服用している降圧剤の種類と服用するED薬によっては併用は避けなければなりません。

薬の作用がマッサージの効果に影響を与えたり、マッサージが薬の作用に影響を与えることはないと考えられます。そのため、薬の服用中にマッサージを受けたとしても、何も問題ありません。

グレープフルーツジュースと高血圧薬の併用は危険なため厳禁ですが、グレープフルーツジュースを飲んだ時の影響は数日持続するとされています。そのため、毎日服用する必要がある高血圧薬を使っている場合には、基本的に服用期間中はずっと避けるべきといえます。ただし、高血圧薬の種類によってはグレープフルーツジュースを飲んでも問題がない場合もあります。

高血圧が原因となって動脈硬化を引き起こし、脳梗塞や脳出血、心筋梗塞などさまざまな病気に繋がってしまいます。高血圧の状態のまま放置すると命のリスクにも繋がるため、治療薬を用いて改善するべきだと言えます。

高血圧の治療薬の中には副作用として生理不順が報告されているものがあります。また、副作用については個人差があるため、副作用があらわれたりあらわれなかったりします。酷い副作用があらわれたような場合には、医師に相談するなどしてください。

| 1日の服用回数 | 3回 |

|---|---|

| 1回の服用量 | 10mg |

| 服用のタイミング | 指定なし |

| 服用間隔 | 指定なし |

| 商品名 | エクセンタ | グロピールリタード | サイアムドパ | セレペグ | ロプレソール | ケルロン |

|---|---|---|---|---|---|---|

| 商品画像 |  |  |  |  |  |  |

| 特徴1 | ・従来品より他のホルモンに影響を与えにくい | ・優れた安全性で幅広い世代の方が服用可能 | ・交感神経に作用して血圧を下げる | ・ウプトラビと同一成分のジェネリック | ・心拍を抑えて心臓の負担を軽減 | ・持続性に優れているβ遮断薬 |

| 特徴2 | ・臓器保護作用にも期待できる | ・他の種類の降圧薬に比べて降圧作用に優れている | ・糖尿病がある方や妊娠中でも服用できる | ・1回の服用で長時間効果が持続 | ・心筋梗塞や脳卒中の予防にも有効 | ・心拍数を正常な状態に整え、降圧作用を示す |

| 内容量 | 25mg100錠x1箱 | 20mg30錠x1箱 | 125mg100錠x1箱 | 200mcg10錠x1箱 | 100mg40錠x1箱 | 20mg14錠x1箱 |

| 価格 | 8,660円 | 4,760円 | 4,160円 | 4,960円 | 6,560円 | 4,460円 |

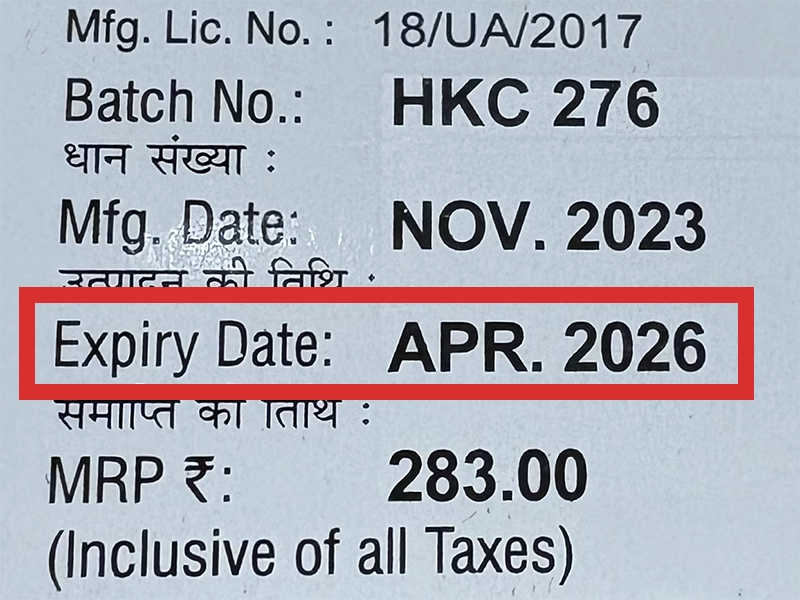

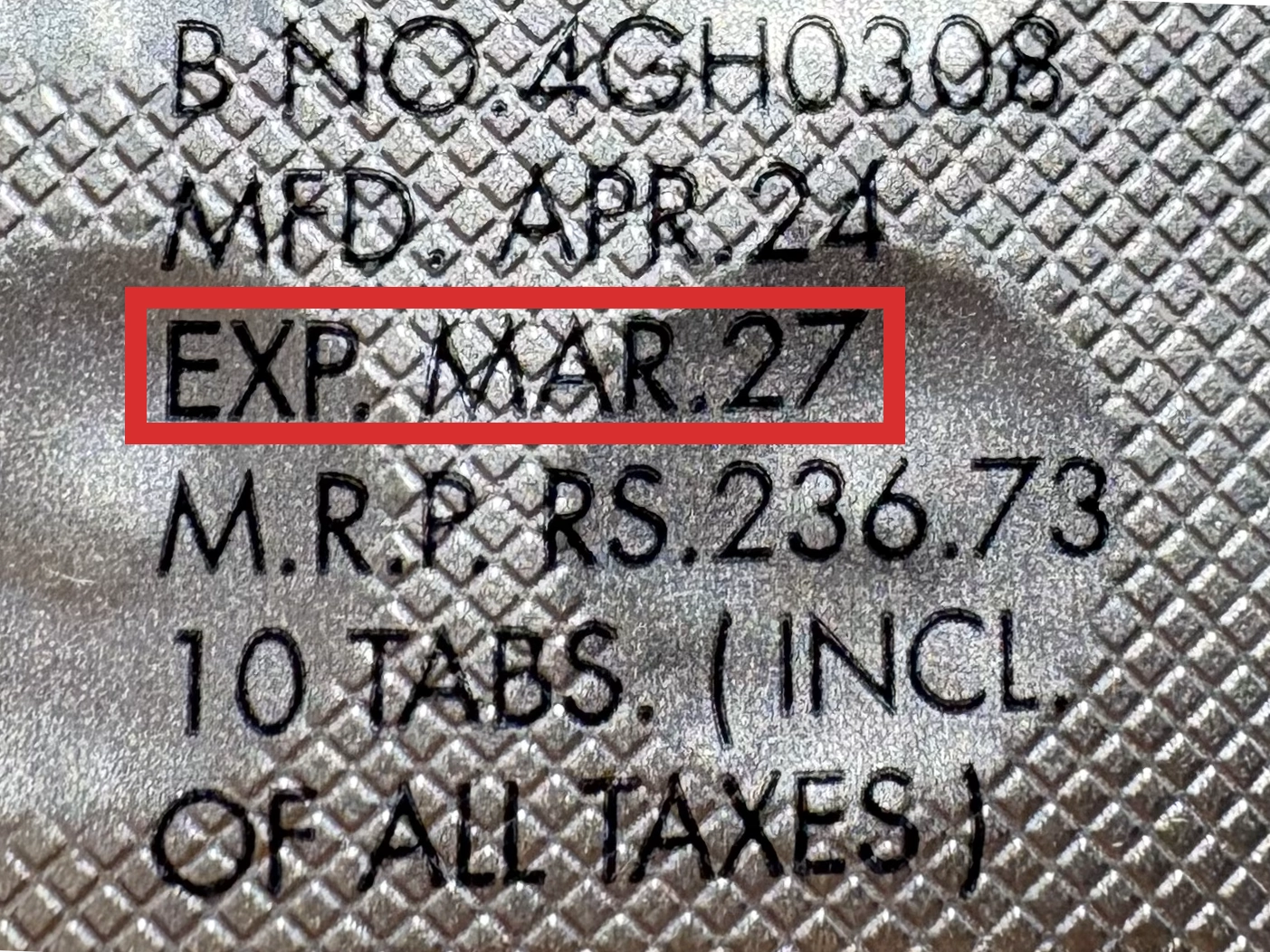

本製品は海外製のため、期限表記が日本と異なる場合がございます。

パッケージ裏面や側面、シートなどに以下のような表記がされています。

| EXP | 使用期限 例:EXP 12/2025→2025年12月まで使用可 |

|---|---|

| MFG または MFD | 製造日 例:MFG 03/2023 |

| BEST BEFORE | 品質が最も安定している目安日 |

※国や製品により日付の並び(例:月/年、日/月/年)が異なる場合がありますのでご注意ください

EXP(Expiry Date) の表記がなく、MFG または MFDしか記載がないケースがあります。

この場合は MFG(MFD) から2~3年が使用期限の目安です。

※「LOT」や「BATCH」の表記は製造番号であり期限ではありません。

パッケージ例となります。

商品やご注文単位によってはシート単位でのお届けとなる場合が御座います。

外箱に当サイト名や商品名が記載されることはないため、ご家族や配達員など第三者に内容を知られることは御座いません。

ニディカードを服用するようになって血圧が標準値に近づきました、このまま継続すれば標準値に戻れそうです。少しだけ顔に赤みが出ますがすぐ落ち着くので問題なさそうです。

「有効性と安全性」「高齢者の方でも」の言葉に惹かれました。血圧の薬は検診の数値で効果を確認できるので、実感できてわかりやすい。今回も良い結果だったので家族も安心してくれています。

安心して使える薬の1つ。いろいろな薬を飲みましたがこれが1番副作用を気にせずに飲めました。血圧の数値も安定してきて効果もしっかりありました。1日1回の服用で済ませれば言うことなしです。

少しでも安全に使えそうなものがいいなと思って、最終的にニディカードにしました。ケースと同じオレンジ色の薬でなんか毒々しそうな雰囲気でしたが、そんな派手な見た目とは裏腹に体にすごく優しく効いてくる感じ。少しずつ血圧が下がっていき、今は正常な値までやってきました。これなら初めて降圧剤を飲むのが不安な方にとっても、選びやすい薬だと私は思いますね。

少し前までネットで購入したニディカードを飲んでいました。長い間飲んでいて1年半以上は飲んでいたと思います。おかげで血圧はかなり下げることができて、今は少し弱めの降圧剤を飲むようにしています。このように薬を変えることができたのも、前に飲んでいたニディカードがしっかり血圧を下げてくれたからだと思います。降圧剤としては高い効果があるので高血圧の方にオススメです。

商品口コミの投稿は会員のみ行えるようになっております。

お手数ですが会員ログインの上でご投稿頂きますようお願いいたします。

口コミをご投稿頂いたお客様にはポイントをプレゼントさせて頂いております。

文章のみであれば100ポイント、文章+写真付きのものは300ポイントをプレゼントさせて頂きます。

規約や詳細などはこちらをご確認くださいませ。